PCI Express IP

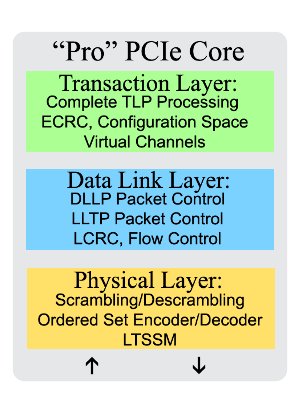

Touit offers a Standard PCI Express (PCIe) core with low resource utilization and low transmit and receive latencies. The Standard PCIe core handles all of the PCIe layer implementation details with user access to the entire Transaction Layer Packet (TLP). In certain applications, which require optimized to real-time communication, access to the Transaction Layer Packet can be an advantage.

For these more demanding applications, Touit can custom-design the interface to fit your needs, or provide tech/engineer support for those designing their own interfaces.

For general applications, add on Touit's Pro core processing layer with its parallel bus interface to manage TLP details and configure DMA channels.

Using Touit's Pro core interface is similar to using a PCI to local bus bridge chip such as the PLX 905x or AMCC 593x. When migrating an existing design from a PCI bridge chip to PCI Express, often times only a larger FPGA with a SERDES is required.

The FPGA design, interface, and implementation are all simplified with the Touit Pro core. For example: there are no input or output pin timing constraint requirements, no board level routing requirements, no additional power supplies, and one less chip to procure and solder on the board. This can lower the overall board cost and reduce time-to-market.